## Überprüfung von Entwurfsregeln auf Package-Ebene mit KLayout

Der Layoutentwurf integrierter Schaltungen (ICs) überführt eine Netzliste in geometrische Maskendaten, die danach zur Herstellung der Chips in einer Halbleiterfabrik verwendet werden. Eine wichtige Teilaufgabe beim Layoutentwurf ist die Verifikation der Entwurfsdaten, z. B. durch den DRC (engl. design rule check) bei dem die Einhaltung der Entwurfsregeln überprüft wird. Bei der Integration mehrerer ICs in einem Package ergeben sich zusätzliche Entwurfsregeln in Abhängigkeit von der gewählten Aufbau- und Verbindungstechnik und den Technologien der beteiligten ICs.

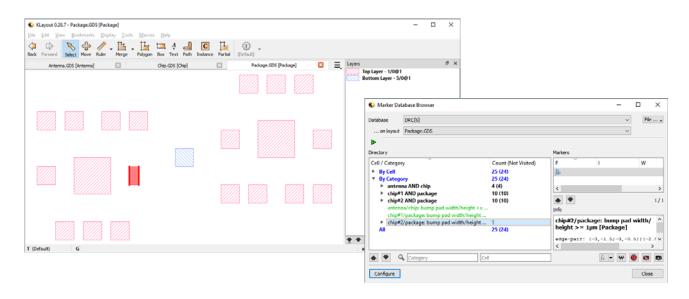

Das Open-Source-Programm KLayout erlaubt neben der Anzeige und Bearbeitung von Maskendaten auch die Überprüfung von Entwurfsregeln mittels eines DRC-Skripts. In einer Studienarbeit wurden die Beschreibung eines Package-Aufbaus mittels JSON-Dateien sowie die automatische Generierung des KLayout-DRC-Skripts durch ein einfaches Python-Programm umgesetzt.

In dieser Aufgabe soll untersucht werden, wie diese Funktionalität auch direkt über ein DRC-Skript umgesetzt werden kann. Dadurch könnte direkt nach einer Veränderung der JSON-Dateien der DRC auf Package-Ebene ausgeführt werden. Es sind die dafür notwendigen Teilschritte zu ermitteln. Das Konzept ist mit Beispielquelltext in einer schriftlichen Projektarbeit festzuhalten.

Anzahl möglicher Bearbeiter: 2-3

Betreuer: Dr.-Ing. Andreas Krinke

Raum BAR II/27

Tel.: 0351 / 463 34705

andreas.krinke@tu-dresden.de