## Fakultät Elektrotechnik und Informationstechnik

# Einführung in das Schaltkreisentwurfssystem Tanner EDA Tools

- I. Eingabe eines Schaltplans

- II. Simulation

- III. Export der Netzlisten

- IV. Layoutentwurf

- V. Verifikation

- VI. Export der Herstellungsdaten

BAR II/27 • Tel.: (0351) 463 34705 • andreas.krinke@tu-dresden.de

# **Einführung**

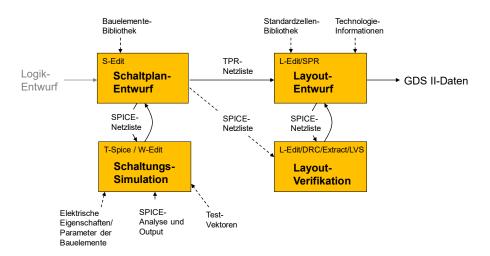

Die Tanner EDA Tools von Siemens bilden ein Schaltkreisentwurfssystem für digitale, analoge und Mixed-Signal-Schaltkreise. Das System beinhaltet mehrere Softwarewerkzeuge für das Zeichnen von Schaltplänen, die Logik- und Timing-Simulation, den Layout-Entwurf und die Layout-Verifikation. Einen Überblick bietet die folgende kurze Beschreibung.

## S-Edit (Schematic Editor – Grafische Eingabeoberfläche zur Schaltplanerstellung):

S-Edit ist eine grafische Entwurfsoberfläche für die Eingabe von Schaltplänen und für deren Analyse. Hier können eigene Module entworfen oder vorgefertigte Module aus Bibliotheken wiederverwendet werden. Die mit dem Schaltplan erstellten Ausgabedaten können zur Simulation (T-Spice), zum Layoutentwurf (L-Edit) und zur Verifikation (LVS) verwendet werden.

#### T-Spice (Circuit Simulator - Schaltungssimulator):

T-Spice ist ein Schaltungssimulator für den IC-Entwurf. Als Eingangsdaten verwendet T-Spice Textdateien. Diese beinhalten neben den Netzlistendaten auch Simulationsbefehle. Diese Dateien können mit einem Texteditor erzeugt werden, lassen sich aus S-Edit exportieren oder mit L-Edit aus einem bestehenden Layout extrahieren.

## W-Edit (Waveform Viewer – Betrachter für Signalverläufe):

Mit W-Edit können die in T-Spice simulierten Größen visualisiert werden. Es sollte daher während der Simulation von T-Spice aufgerufen werden, um Simulationsergebnisse darzustellen.

#### L-Edit (Layout Editor – Grafische Eingabeoberfläche zur Layouterstellung):

Für die Schaltkreisproduktion notwendige Masken können mit dem grafischen Entwurfswerkzeug L-Edit erstellt werden. Die Masken werden in Layern verwaltet. Die Maskendaten werden als GDS II- oder CIF-Dateien ausgegeben.

#### L-Edit/SPR (Standard Cell Place & Route – Platzierung und Verdrahtung von Standardzellen):

L-Edit/SPR wird innerhalb von L-Edit verwendet, um aus einer schaltungsspezifischen Netzliste, einer Technologiedatei und einer Standardzellenbibliothek ein Standardzellen-Layout zu generieren. Die schaltungsspezifische Netzliste wurde zuvor von S-Edit erzeugt. Sie enthält eine Beschreibung des Designs in Textform und die Verknüpfungen mit den verwendeten Standardzellen.

#### L-Edit/DRC (Design Rule Check - Überprüfung der Entwurfsregeln):

L-Edit/DRC ist ein Werkzeug, das die Einhaltung von technologischen Entwurfsregeln überprüft. Regelverstöße können direkt im Layout dargestellt oder in einer Textdatei ausgegeben werden.

## L-Edit/Extract (Extraktion einer Netzliste aus dem Layout):

Durch Extraktion kann aus einem fertigen Layout eine beschreibende Netzliste erzeugt werden. Diese Netzliste liegt im Berkeley-PSpice-Format vor, das von T-Spice und zum LVS-Netzlistenvergleich (s. u.) verwendet werden kann.

#### LVS (Layout vs. Schematic - Vergleich von Layout und Schaltplan):

LVS gestattet den Vergleich von Netzlisten. Dadurch kann festgestellt werden, ob ein Layout einem Schaltplan entspricht. Die Eingabe bilden zwei Spice-Netzlisten, die aus S-Edit und L-Edit (mittels L-Edit/Extract) exportiert werden.

# Übungsablauf

In dieser Übung soll der standardzellenbasierte Entwurf digitaler Schaltkreise mit dem Entwurfssystem "Tanner EDA Tools" trainiert werden. Die folgenden Schritte sind dafür notwendig:

- I. Eingabe des Schaltplans der gewünschten Schaltung in S-Edit.

- II. Simulation der Schaltung im Schaltungssimulator **T-Spice** mit grafischer Ausgabe der Signalverläufe in **W-Edit**.

- III. Export von TPR-Netzliste (für die Layouterstellung) und SPICE-Netzliste (für LVS) aus S-Edit.

- IV. Layoutentwurf

- 1. Verwendung des Layout-Werkzeugs L-Edit.

- Auswahl der Technologiedatei, der TPR-Netzliste und der zu verwendenden Standardzellenbibliothek.

- 3. Bestimmung der Eigenschaften des Padframes.

- 4. Automatischer Layoutentwurf mit L-Edit/SPR.

- V. Verifikation: Prüfung auf Einhaltung der technologischen Regeln mit **L-Edit/DRC**, Generierung einer Netzliste aus dem Layout mit **L-Edit/Extract**, Vergleich der aus dem Layout und aus dem Schaltplan erzeugten Netzlisten mit **LVS**.

- VI. Export der GDS II-Daten für die IC-Herstellung aus L-Edit.

## Übersicht:

# **Nutzungshinweis zu Tanner Tools:**

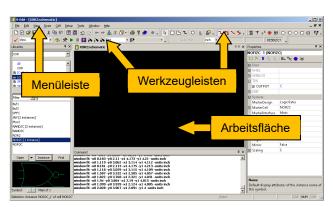

Die Oberflächen sämtlicher Tanner-Werkzeuge unterteilen sich in Menüleiste, Arbeitsfläche und mehrere Werkzeugleisten.

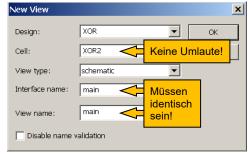

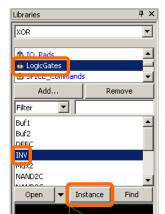

Es sollten keinesfalls Umlaute zur Benennung von Dateien, Bibliotheken, Module usw. verwendet werden!

# I. Eingabe des Schaltplans mit S-Edit

S-Edit unterscheidet zwei grundsätzliche Darstellungsarten:

- Schaltplan-Darstellung (Schematic Mode) zur Erzeugung eines Schaltplans.

- Symbol-Darstellung (Symbol Mode) zur Erstellung von Schaltplansymbolen.

Der Modus kann durch Klicken auf das jeweilige Symbol 🖻 🖾 in der Menüleiste umgestellt werden.

#### Schritt 1: Erstellen eines einfachen Moduls

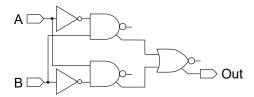

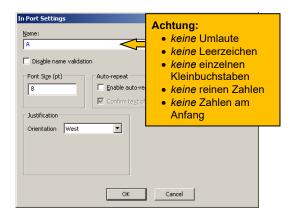

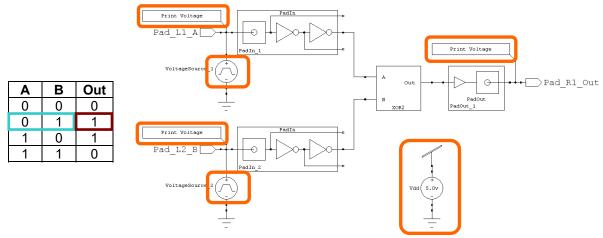

In diesem Schritt wird der nebenstehende Schaltplan mit zwei Eingängen, einem Ausgang, zwei Invertern, zwei AND-Gattern und einem OR-Gatter erzeugt.

- 1. Start des Programms S-Edit und Anlegen eines neuen Designs:

- Start von S-Edit, Erstellen des Designs mit File

New

New Design. Benennen des Designs als "XOR". Es wird automatisch eine gleichnamige Bibliothek erstellt. Alle später selbst erstellten Module sollten in dieser Bibliothek angelegt werden.

In das Feld "Create in Folder" wird der Pfad eingetragen, in dem das Design erstellt werden

D:\Tanner\Libraries\All\All.tanner

OK

soll (jetzt "**D:\Tanner**\", für das eigentliche Projekt z. B. das "Dokumente"-Verzeichnis)<sup>1</sup>.

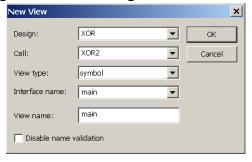

Erstellen eines neuen Schematic-Views mit Cell -> New View. Die verschiedenen Felder sind wie in der nebenstehenden Abbildung gezeigt auszufüllen.

**Hinweis:** Die Namen des Designs und des Moduls sollten unterschiedlich sein.

Cancel

- 2. Laden der Bauelementebibliothek:

- Laden der Bibliothek mit

File → Open → Add Library.

- Auswahl der Bibliothek "All.tanner" aus dem Verzeichnis "D:\Tanner\ Libraries\All". Dadurch werden automatisch alle notwendigen Bibliotheker

matisch alle notwendigen Bibliotheken hinzugefügt².

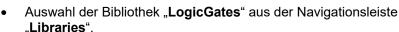

- 3. Auswahl und Platzierung von Instanzen:

- Auswahl des Gatters "INV" und klicken auf "Instance". Es öffnet sich das Dialogfenster "Instance Cell". Hier kann z. B. ein neuer Name eingeben werden.

- Die Vergrößerung des Schaltplans kann per Mausrad oder mit den Tasten +/

– angepasst werden.

- Klicken auf die Position auf der Zeichenfläche, an der das Gatter erzeugt werden soll. Es werden zwei Inverter benötigt. Ein Klick auf "Done" schließt das Dialogfenster.

Symbol: 🕕 Main of 1

<sup>&</sup>lt;sup>1</sup> **Achtung:** Das Verzeichnis "D:\Tanner\" nicht zum dauerhaften Speichern von Daten verwenden! Es könnte durch einen anderen Benutzer oder nach einem Neustart gelöscht werden! Daher Daten vor dem Ausloggen z. B. auf **Z:\** kopieren.

<sup>&</sup>lt;sup>2</sup> Die Datei "libraries.list" im Projektverzeichnis enthält die Verweise auf alle geladenen Bibliotheken. Sollten Bibliotheken nicht gefunden werden ("unresolved libraries"), sind die Pfade in dieser Datei zu ändern.

- Wiederholung dieses Vorgangs f

ür die Gatter "NAND2C" und "NOR2C".

- Anordnen der Gatter wie oben abgebildet. Die Elemente lassen sich dazu mit der rechten oder linken Maustaste auswählen und durch Klicken und Halten der mittleren Maustaste verschieben (auch mit Alt + linke Maustaste möglich)<sup>3</sup>.

#### 4. Erstellen von Ports:

• Erstellen von Eingangsports über das Symbol □ (Werkzeugleiste) und Klicken auf die Position auf der Zeichenfläche, an der das Symbol erzeugt werden soll. Es öffnet sich das Dialogfenster "In Port Settings", in dem als Name "A" eingetragen und der Vorgang mit "OK" bestätigt wird. Mit der Taste "R" kann das Symbol danach rotiert werden.

- Wiederholen des Vorgangs für den Eingangsport "B".

- Erstellen des Ausgangsports "Out" nach Anwahl des Symbols □ und Klicken auf die Zeichenfläche an der gewünschten Position. Gegebenenfalls Beenden der Port-Eingabe durch Klick auf ト.

- 5. Verbinden der Gatter mit den Ein- und Ausgangsports:

- Auswahl des Verdrahtungssymbols

in der Schaltplan-Werkzeugleiste.

- Die Verdrahtung wird mit der linken Maustaste gestartet und mit der rechten Maustaste beendet.

- Verdrahten der Schaltung wie abgebildet. Der Verdrahtungsmodus wird mit einem Klick auf das Symbol oder über die Taste "ESC" beendet.

• Alternativ können zwei grafisch unverbundene Teilnetze auch elektrisch verbunden werden, indem sie die gleiche Bezeichnung (Net Label, Symbol: 💯) zugewiesen bekommen.

Test: Verdrahtung des Netzes zwischen einem NAND2C und NOR2C per Net Label.

## Schritt 2: Erstellen eines Symbols für die eingegebene Schaltung

Jede Schaltung kann durch ein Symbol repräsentiert werden, um die Schaltung in einer höheren Hierarchieebene verwenden zu können.

Erstellen eines neuen Symbol-Views mit Cell → New View. Die verschiedenen Felder sind wie in der nebenstehenden Abbildung auszufüllen.

<sup>&</sup>lt;sup>3</sup> Mit den Tasten + und – oder mit dem Mausrad kann die Ansicht vergrößert bzw. verkleinert werden. Besonders praktisch ist die Taste **Pos1** / **Home**, da hier die Bildgröße automatisch angepasst wird. Mit den Pfeiltasten ist die Bewegung innerhalb des Arbeitsbereichs möglich.

- 2. Zeichnen eines Rechtecks nach Klick auf das Symbol □.

- 3. Erstellen der Ein- und Ausgangsports ("A", "B", "Out") wie zuvor beschrieben (Symbole und ). Dabei muss beachtet werden, dass die gleichen Namen wie im Schaltplan (siehe Schritt 1.4) verwendet werden.

- A DA Out Dut B XOR2

- 4. Nach Auswahl des Symbols L können die Beschriftungen des Moduls (A, B, Out) hinzugefügt werden.

- 5. Mit dem Pfad-Werkzeug ( ) kann das Rechteck mit den Ports verbunden werden. Die linke Maustaste beginnt das Zeichnen von Linien, die rechte beendet es.

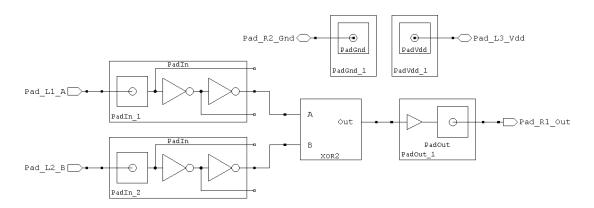

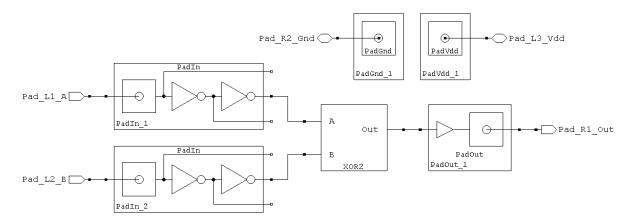

## Schritt 3: Erstellen des Top-Level-Moduls

Das Top-Level-Modul besteht aus:

- Einer Instanz des zuvor erstellten Moduls "XOR2".

- Zwei Eingangspads mit je einem Eingangsport.

- · Einem Ausgangspad mit einem Ausgangsport.

- Einem Massepad mit einem bidirektionalen Port.

- Einem Betriebsspannungspad mit einem bidirektionalen Port.

Die Pads sind Anschlussflächen für die Außenanschlüsse des Schaltkreises.

#### Erstellen des Top-Level-Moduls:

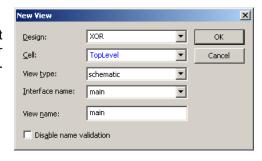

- 1. Generieren eines neuen Top-Level-Moduls:

- Erstellen eines neuen Schematic-Views mit Cell -> New View. Die verschiedenen Felder sind wie in der nebenstehenden Abbildung auszufüllen.

- 2. Erzeugen einer Instanz des "XOR2"-Moduls:

- Auswahl der Bibliothek "XOR" aus der Navigationsleiste "Libraries". Auswahl des Moduls "XOR2" und klicken auf den Button "Instance". Dadurch öffnet sich das Dialogfenster "Instance Cell".

- Klicken auf die Position auf der Zeichenfläche, an der die Gatter erzeugt werden sollen (gegebenenfalls zoomen). Anschließend das Dialogfenster "Instance Cell" mit "Done" schließen.

- 3. Platzieren von zwei Eingangs- und einem Ausgangspad ("Padln" bzw. "PadOut") aus der Bibliothek "IO Pads".

- 4. Platzieren je einer "PadGnd"- und "PadVdd"-Instanz. Diese befinden sich ebenfalls in der Bibliothek "IO\_Pads". Erstellen von zwei Eingangsports, zwei bidirektionalen Ports und des Ausgangsports wie zuvor beschrieben. Benennung der Eingangsports als "Pad\_L1\_A" bzw. "Pad\_L2\_B", der bidirektionalen Ports als "Pad\_L3\_Vdd" bzw. "Pad\_R2\_Gnd" und des Ausgangsports als "Pad\_R1\_Out".

**Hinweis:** Mit der Bezeichnung der Ports lässt sich die gewünschte Lage eines Pads in dem zu erzeugenden Layout angeben. Die Nummerierung erfolgt dabei entgegen dem Uhrzeigersinn, wobei sich "Pad\_L1\_A" links oben und "Pad\_R1\_Out" rechts unten im Padframe befinden (siehe auch die Dokumentation der Tanner Tools). Die Pads zur Spannungsversorgung (Vdd, Gnd) müssen **immer** an gegenüberliegenden Seiten des Schaltkreises angeordnet werden, damit die Standardzellen von beiden Seiten erreicht werden können. Empfehlenswert ist ihre Anordnung auf der linken und rechten Seite, da andernfalls der Schaltkreis aufgrund zusätzlich notwendiger Power-Rails höher wird.

5. Abschließend werden alle Elemente mit dem Verdrahtungs-Werkzeug (₺) verbunden.

6. Abspeichern des Designs (File → Save → Save Design XOR).

**Hinweis:** Durch einen Doppelklick auf ein Symbol, z. B. das des XOR2-Moduls, wird der zugehörige Schaltplan geöffnet. Alternativ kann nach der Auswahl eines Moduls per Klick auf das Symbol & die nächste Hierarchie-Ebene angezeigt werden. Die nächsthöhere Ebene bis hin zum Toplevel-Modul wird durch Doppelklick auf einen leeren Bereich der Zeichenfläche erreicht (Alternative: Klicken auf das Symbol ).

Jetzt kann aus dem Design eine Netzliste erzeugt werden. Diese dient später als Grundlage für die Platzierung und die Verdrahtung in L-Edit. Vorher ist es jedoch sinnvoll, das Design durch Simulation zu überprüfen. Mit diesem Schritt befasst sich der nächste Abschnitt.

## II. Simulation

Durch Logiksimulation kann bereits vor dem Erstellen des Layouts die logische Funktion simuliert und überprüft (verifiziert) werden. Dazu kommt im Hintergrund das Programm T-Spice zum Einsatz.

Die hier behandelte Beispielschaltung wird durch die Logiktabelle links im Bild beschrieben. Zur Verifikation wird (soweit möglich) für jeden Eingangszustand ein Testvektor (z.B. 🔲) an die Eingänge "A" und "B" angelegt und geprüft, ob sich der Ausgang "Out" wie gewünscht verhält (im Beispiel 🗖).

Zur Simulation werden zusätzliche Elemente im Schaltplan benötigt.

- Alle Signale, die mit einer Instanz des Moduls "Print Voltage" verbunden sind, werden später in W-Edit angezeigt. In dieser Übung kommen die Eingangs- und Ausgangssignale "Pad L1 A", "Pad\_L2\_B" und "Pad\_R1\_Out" in Frage.

- Es werden Spannungsquellen zur Erzeugung der Zustände für die Testvektoren benötigt. Dafür gibt es unterschiedliche Methoden, z.B. die Verwendung von Rechteckquellen mit unterschiedlicher Pulsweite und Frequenz. Zu Beginn sind alle Signale logisch 0, so dass an beiden Eingängen eine 0 anliegt. Als nächstes wird die Rechteckquelle mit der kürzesten Periodendauer logisch 1 (in diesem Fall "VoltageSource 1"), so dass der Testvektor 01 anliegt, usw. Eine weitere Möglichkeit ist die Benutzung einer binären Spannungsquelle (Bit) mit passenden Bitmustern.

- Zusatzschaltungen können die spätere Signalauswertung vereinfachen. Zum Beispiel ist es möglich, Zählerausgänge per Widerstandsleiter (DA-Wandler) als ein einzelnes Signal auszugegeben.

- Die notwendige Betriebsspannung wird durch die Spannungsguelle "Vdd" bereitgestellt.

## Schritt 1: Einrichten der Simulation

Die Simulation einzelner Module erfolgt durch Erzeugen eines neuen Schematic-Views namens *Modulname\_*Testbench. Darin werden eine Instanz des Moduls, erforderliche Pad-Zellen und die übrigen Elemente einer Testbench erzeugt. Der Einfachheit halber wird hier die XOR2-Testbench auf Basis des eben erstellten Moduls "TopLevel" erstellt.

- 1. Auswahl des Moduls "TopLevel" aus dem Design "XOR".

- Erzeugen einer Kopie des Moduls "TopLevel" mit Cell → Copy Cell. Der neue Name ist "XOR2 Testbench".

- 3. Das Modul "XOR2\_Testbench" wird nach dem Kopieren automatisch geöffnet.

- Copy dependencies None Needed only C All Preview... Disable name validation

Copy Cell

Design:

Cell name:

XOR

TopLeve

XOR2\_Testbench

OK

Cancel

▼

**T**

▾

-

4. Entfernen der beiden Padzellen "PadGnd\_1" und "PadVdd\_1" und der zugehörigen Ports.

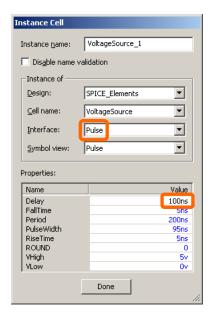

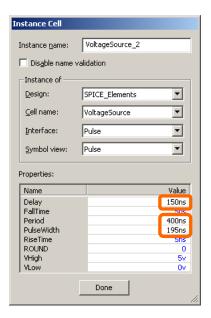

5. Auswahl und Platzieren der zwei Rechteckquellen "VoltageSource\_1" und "Voltage-Source\_2" aus der Bibliothek "SPICE\_Elements". Dazu soll im Feld "Interface" die Option "Pulse" ausgewählt werden. Die "Properties" sind wie folgt auszufüllen:

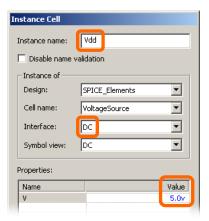

- 6. Auswahl und Platzieren der Quelle "Vdd". Dazu wird "SPICE\_Elements" → "Voltage Source" gewählt. Im Feld "Interface" soll die Option "DC" ausgewählt werden.

- 7. Auswahl des Massesymbols "**Gnd**" und des Betriebsspannungssymbols "**Vdd**" aus der Bibliothek "**Misc**" und platzieren gemäß der Abbildung oben.

- 8. Auswahl und Platzieren der drei "**Print Voltage**"-Instanzen aus der Bibliothek "**SPICE\_Commands**". Verbinden der Symbole mit den Eingangs- und Ausgangssignalen.

- Auswahl des Symbols

und Verbinden aller Symbole gemäß der Abbildung oben.

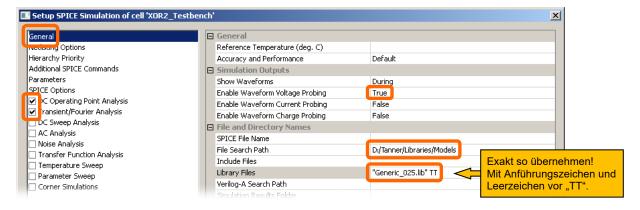

- 10. Die Festlegung der Simulationsparameter erfolgt mit "**Setup → SPICE Simulation**". Es öffnet sich ein Dialogfenster.

- Option "General" auswählen und die verschiedenen Felder wie in der folgenden Abbildung gezeigt ausfüllen.

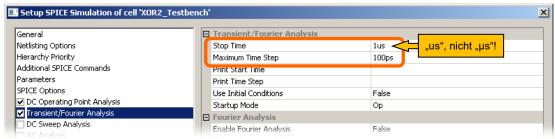

• Option "**Transient/Fourier Analysis**" auswählen und die verschiedenen Felder wie in der folgenden Abbildung ausfüllen.

11. Abspeichern des Designs ("Save Design XOR").

## Schritt 2: Durchführung der Simulation

- 1. Starten des Simulators **T-Spice** durch Klick auf das Symbol ▶ in S-Edit.

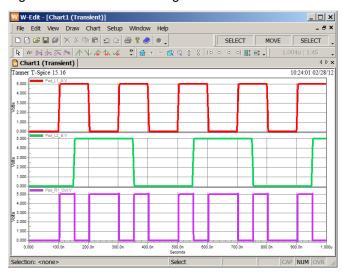

- 2. Es öffnet sich **W-Edit** zur Darstellung der Eingangs- und Ausgangswellenformen. Der Menüpunkt **Chart** → **Expand Traces** weist jedem Signal ein eigenes Diagramm zu. Nun kann das Ausgangssignal überprüft und mit dem gewünschten Resultat verglichen werden.

#### Hinweise:

- Durch Auswahl des "**Probe-Voltage**"-Symbols (\*\*) in S-Edit kann jedes Signal durch Klick auf das zugehörige Netz angezeigt werden, z. B. zur Fehlersuche.

- Diagramme können per Rechtsklick und Auswahl von "Move Plot" neu angeordnet werden.

- · Ausdruck im Querformat ist nicht möglich.

- Das Speichern von Simulationsergebnissen, so dass sie später wieder in W-Edit geöffnet werden können, ist mit folgender Vorgehensweise möglich:

- (1) In den Simulationseinstellungen in S-Edit unter "General", "Simulation Results Folder" einen Ausgabepfad speziell für das aktuelle Modul festlegen.

- (2) Unter diesem Pfad wird automatisch ein Verzeichnis <Name des Moduls>, sowie eine Datei <Name des Moduls>.tsim erzeugt.

- (3) Simulationsergebnisse in diesem Verzeichnis werden bei jeder Simulation überschrieben, es sei denn, in den Simulationseinstellungen wird die Option "Keep all simulation results" auf True gesetzt.

- (4) Das Chartbook von W-Edit sollte ebenfalls in diesem Pfad neben der tsim-Datei gespeichert werden.

- 3. Schließen von W-Edit und T-Spice.

- 4. Abspeichern des Designs ("Save Design XOR").

# III. Exportieren der Netzlisten

Aus dem simulierten Schaltplan wird eine Netzliste im TPR-Format (Tanner Place and Route) erzeugt. Diese wird vom Layoutwerkzeug L-Edit/SPR (Standard Cell Place and Route) verwendet, um das Layout zu erzeugen.

Aus dem Schaltplan wird weiterhin eine Netzliste im SPICE-Format erstellt, die für den nachfolgenden Verifikationsschritt (LVS) benötigt wird.

#### Vorgehensweise:

- 1. Auswahl des Designs "XOR" aus der Navigationsleiste "Libraries".

- 2. Öffnen des Moduls "TopLevel" (nicht der Testbench) durch Doppelklick.

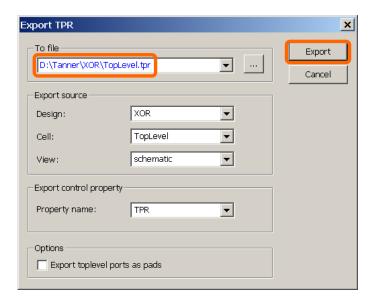

- 3. Exportieren der TPR-Netzliste mit File → Export → Export TPR

- 4. In dem neuen Dialog wird als Dateiname "**TopLevel.tpr**" eingetragen. Ein Klick auf "**Export**" schließt das Fenster.

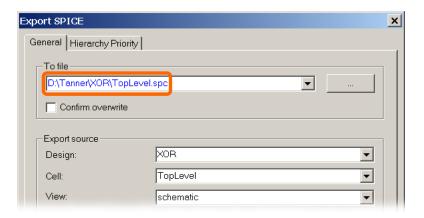

5. Die SPICE-Netzliste wird über **File → Export → Export SPICE** erzeugt. Eine eventuell vorhandene alte Datei kann überschrieben werden.

6. Schließen von S-Edit.

# IV. Layoutentwurf

Nun wird L-Edit/SPR (*Standard Cell Place and Route*) verwendet, um das Layout des Designs zu generieren. Die Layouterstellung beinhaltet das Platzieren (*Placement*) und Verdrahten (*Routing*) der Standardzellen und Außenanschlüsse (*Pads*).

- 1. Kopieren aller Bibliotheksdateien aus dem Verzeichnis "D:\Tanner\Libraries\Tech Files\" in das aktuelle Design-Verzeichnis (z. B. "D:\Tanner\XOR\").

- 2. Start des Programms L-Edit.

- 3. Auswahl der Technologiedatei, der Netzliste und der Standardzellenbibliothek:

Zuerst werden die Technologie-Informationen durch Auswahl von File → Replace Setup importiert.

Im Dialogfenster wird nach Klick auf "Browse" die Datei "**Tech\_Info.tdb**" im aktuellen Verzeichnis lokalisiert.

Verlassen des Fensters mit "OK". Die ausgegebene Meldung nochmals mit "OK" bestätigen.

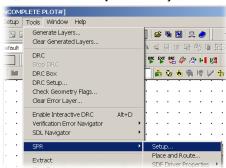

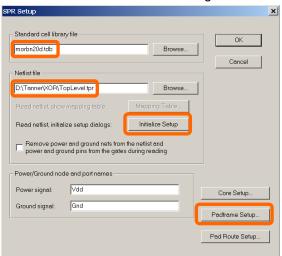

Durch Auswahl von **Tools** → **SPR** → **Setup** wird das Dialogfenster "**SPR Setup**" geöffnet. Hier wird als Standardzellenbibliothek "**morbn20d.tdb**" und als Netzliste "**TopLevel.tpr**" eingetragen.

Mit "Initialize Setup" werden jetzt die Standardzellenbibliothek und die Netzliste geladen.

4. Bestimmung der Eigenschaften des Padframes<sup>4</sup>.

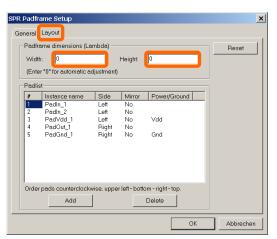

Auswahl von "Padframe Setup", um den Dialog "SPR Padframe Setup" zu öffnen.

In der Registerkarte "Layout" können die Abmessungen des Padframes bestimmt und die Lage der Pads geprüft werden.

Unter "Padframe dimensions" wird die gewünschte Breite ("Width") und die Höhe ("Height") des Padframes eingegeben. Wird hier jeweils 0 angegeben, werden Breite und Höhe automatisch festgelegt.

<sup>&</sup>lt;sup>4</sup> Der Padframe ist der äußere Rahmen, auf dem sich alle Außenanschlüsse (Pads) befinden. Er stellt die Verbindung zur "äußeren Welt" dar – z. B. zur Leiterplatte (bei Nacktchip-Verarbeitung) oder zu den Schaltkreis-Anschlussbeinen (bei gehäustem Chip).

Die "**Padlist**" gibt die Lage der Pads an. Die Nummerierung (Spalte "#") erfolgt dabei gegen den Uhrzeigersinn, wobei sich Pad 1 links oben im Padframe befindet.

Durch zweimaliges Klicken auf "OK" werden eventuelle Änderungen übernommen.

#### 5. Automatischer Layoutentwurf in L-Edit/SPR:

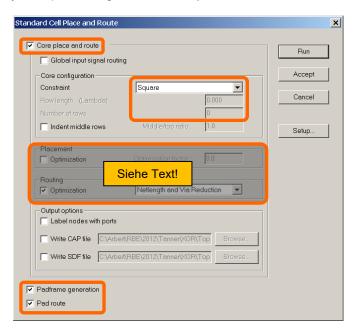

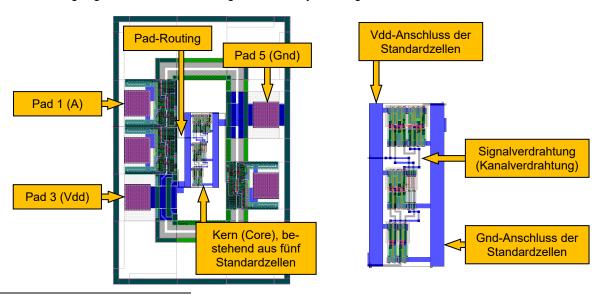

Nach Auswahl von Tools → SPR → Place and Route öffnet sich der Dialog "Standard Cell Place and Route". Um das komplette Layout zu generieren, werden alle drei Module ("Core place and route", "Padframe generation" und "Pad route") ausgewählt (siehe Abbildung). In dieser Einführung wird die Optimierung der Platzierung nicht verwendet. Später sollten unbedingt sowohl die Optimierung der Platzierung als auch die Verdrahtungsoptimierung aktiviert werden. Der Optimierungsfaktor ist dann geeignet im Bereich von 0 bis 10 zu wählen. Die Veränderung der Randbedingung ("Constraint") kann das Layout weiter verkleinern. Weitere Informationen zur Layout-Optimierung sind über Help → Placement and Routing verfügbar.

Der Abschluss von Platzierung und Verdrahtung wird mit einer Meldung quittiert. Nach der Bestätigung durch "**OK**" wird das generierte Layout dargestellt<sup>5</sup>:

<sup>&</sup>lt;sup>5</sup> Mit den Tasten + und - kann die Ansicht vergrößert bzw. verkleinert werden (auch mit dem Mausrad möglich). Am praktischsten ist die Taste **Pos 1**, da hier die Bildgröße automatisch angepasst wird. Mit den Pfeiltasten ist die Bewegung innerhalb des Arbeitsbereichs möglich.

# V. Verifikation des Layouts

Die Layoutprüfung (Verifikation) beinhaltet zwei Schritte:

- Prüfung auf Einhaltung der Technologieregeln: DRC (Design Rule Check)

- Prüfung auf Übereinstimmung mit dem Schaltplan durch Netzlistenvergleich: LVS (*Layout versus Schematic*).

Während der DRC direkt im Layout durchgeführt wird, erfordert der LVS aus dem Schaltplan (S-Edit) und dem Layout (L-Edit) erzeugte SPICE-Netzlisten. Zur Netzlisten-Erzeugung aus dem Layout dient die Extraktion mit L-Edit/Extract. Die dabei zu erkennenden Schaltungselemente sind in ihrer Beschreibung (z. B. als konkrete Ebenenüberlappungen) in einer Extraktionsdatei (extract definition file) festgelegt.

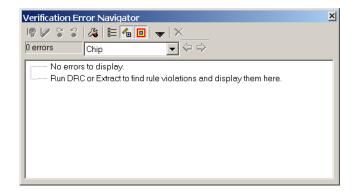

# Schritt 1: Prüfung auf Einhaltung der technologischen Regeln (DRC)

L-Edit/DRC ist ein Werkzeug, das ein Design auf das Einhalten von Entwurfsregeln (z. B. Überlappungen, minimale Breite und minimaler Abstand) hin überprüft. Durch Auswahl von **Tools → DRC** wird die Verifikation gestartet. Nach Abschluss der Verifikation zeigt ein Dialogfenster, ob das Layout die Regeln einhält.

## Schritt 2: Netzlistenvergleich (LVS)

- 1. Generierung einer SPICE-Netzliste aus dem Layout mittels L-Edit/Extract:

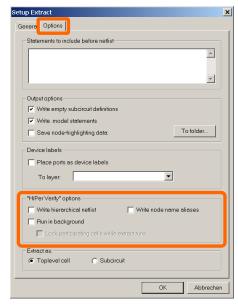

- Zur Konfiguration der Layout-Extraktion, wird **Tools** → **Extract Setup** ausgewählt. Es öffnet sich das Dialogfenster "**Setup Extract**".

- Im Feld "Extract Rule Sets to run" (Liste der Extraktionsdateien) wird die Datei "morbn20.ext" im aktuellen Design-Verzeichnis angegeben.

- Im Feld "SPICE extract output file" (zu erzeugende SPICE-Netzliste) wird "TopLevel\_Layout.spc" eingetragen.

- Auf dem zweiten Reiter "Options" dürfen in der Gruppe "HiPer Verify options" keine Felder ausgewählt werden.

Die Auswahl von **Tools** → **Extract** startet die Extraktion. Dabei auftretende Warnungen über unattached ports und short circuits können ignoriert werden. Im Ergebnis liegt eine Netzliste im SPICE-Format vor, welche das Layout in Form von Bauelementen und Verbindungen beschreibt.

- 2. Abspeichern des Layouts als "XOR\_Layout.tdb" und Schließen von L-Edit.

- 3. Start des Programms LVS.

- 4. Nach Auswahl des Symbols bzw. File → New öffnet sich der Dialog "New File". Dort wird "LVS Setup" ausgewählt und durch "OK" bestätigt.

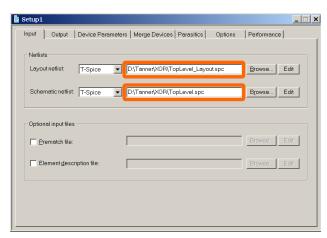

- 5. Es folgt die Definition der zu vergleichenden Netzlisten. Über "Browse" werden die aus dem Layout extrahierte Netzliste "TopLevel\_Layout.spc" und die Netzliste des Schaltplans "TopLevel.spc" ausgewählt.

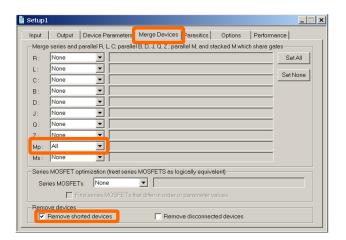

6. Auf dem Reiter "Merge Devices" muss der Eintrag in der Zeile "Mp" auf "All" gesetzt werden. Das bewirkt eine automatische Zusammenfassung paralleler Transistoren, so dass diese zu keiner Meldung über Unterschiede zwischen den Netzlisten führen. Weiterhin muss der Punkt "Remove shorted devices" ausgewählt werden.

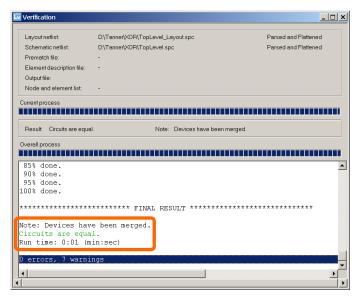

- Nun kann der Netzlistenvergleich durch Klick auf das Symbol ► bzw. Auswahl von Verification → Run gestartet werden.

- Als Ergebnis wird angezeigt, ob die beiden Netzlisten dieselbe Schaltung beschreiben oder ob sie Unterschiede aufweisen.

- 9. Schließen von LVS.

# VI. Export der GDS II-Daten aus L-Edit

Abschließend können die GDS II-Daten aus L-Edit für die IC-Herstellung exportiert werden. Folgende Schritte sind dazu notwendig.

- 1. Start des Programms L-Edit und Öffnen des Designs "XOR\_Layout.tdb".

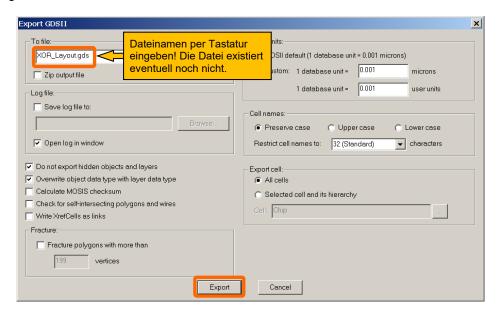

- Nach Auswahl von File → Export Mask Data → GDSII öffnet sich ein Dialogfenster. Dort wird im Feld "To file" der Dateiname "XOR\_Layout.gds" eingetragen. Ein Klick auf "Export" erzeugt die GDS II-Datei.

3. Schließen von L-Edit

## Literatur

Onlinedokumentation der Tanner Tools (unter **Start** → **Programme** → **Tanner EDA** → ... → **Documentation** verfügbar)

# Glossar

| ASIC                    | <br>Application-Specific Integrated Circuit – anwendungs-<br>spezifischer integrierter Schaltkreis – für eine spezielle<br>Anwendung entworfener Schaltkreis           |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contact                 | <br>Durchkontaktierung zum Verdrahtungsanschluss einer Zelle                                                                                                           |

| Core                    | <br>Bereich einer Schaltung, in dem (Standard-)Zellen und ihre<br>Verdrahtung angeordnet sind (ohne Pads / Padanschlüsse)                                              |

| DAC / DA-Wandler        | <br>Digital-Analog-Wandler                                                                                                                                             |

| Gate / Gatter           | <br>Zelle zur Realisierung einer logischen Funktion (z. B. NAND)                                                                                                       |

| GDS II                  | <br>Binäres Dateiformat für Layout-Informationen – wird an den<br>Schaltkreishersteller übergeben                                                                      |

| Gnd / GND               | <br>Ground, Masseanschluss                                                                                                                                             |

| Instance / Instanz      | <br>Virtuelle Modulkopie durch Referenz auf ein Originalmodul (Ableitung eines Bibliotheksmoduls zur Nutzung in Schaltung)                                             |

| Layer                   | <br>Darstellungsebene                                                                                                                                                  |

| Layout                  | <br>Topologische Darstellung der einzelnen Materialebenen eines<br>Halbleiterchips                                                                                     |

| LVS                     | <br>Layout Versus Schematic, Vergleich der Netzlisten von Layout und Schaltplan                                                                                        |

| Mixed-signal (circuits) | <br>Integrierte Schaltkreise, die sowohl digitale als auch analoge<br>Funktionalität beinhalten                                                                        |

| Modul                   | <br>Funktionelle Schaltungseinheit, wie z.B. ein Gatter, ein<br>Verstärker oder auch das komplette Design (Top-Level-<br>Modul)                                        |

| NAND-Gatter             | <br>Gatter, das Eingangssignale mit einem logischen UND verknüpft und dann negiert                                                                                     |

| Netzliste               | <br>Textuelle Beschreibung der Verknüpfung von Bauelementen bzw. Gattern mittels Netzen                                                                                |

| NOR-Gatter              | <br>Gatter, das Eingangssignale mit einem logischen ODER verknüpft und dann negiert                                                                                    |

| Pad                     | <br>Außenanschluss des Schaltkreises                                                                                                                                   |

| Padframe                | <br>Äußerer Ring, auf dem Pads angeordnet werden                                                                                                                       |

| Pad routing             | <br>Verbindung der Außenanschlüsse mit dem Kern (Core)                                                                                                                 |

| Port                    | <br>Symbol für Signalein- und -ausgänge eines Moduls im<br>Schaltplan                                                                                                  |

| Power rail              | <br>Stromversorgungs-/ Masseflächen links und rechts vom Kern                                                                                                          |

| SPICE                   | <br>Simulation Program with IC Emphasis, Simulationswerkzeug                                                                                                           |

| Standardzellen          | <br>Gatter, die zur besseren Reihenanordnung alle dieselbe<br>Höhe besitzen                                                                                            |

| Top-Level(-Modul)       | <br>Oberstes Modul in einer Design-Hierarchie                                                                                                                          |

| TPR (Format)            | <br>Tanner Place and Route Netzlistenformat – enthält die<br>Beschreibung eines Designs in Textform und die<br>Verknüpfungen mit den verwendeten Standardzellen        |

| Via                     | <br>Durchkontaktierung zwischen Metallebenen                                                                                                                           |

| Vdd / VDD               | <br>Stromversorgung der Standardzellen                                                                                                                                 |

| XOR-Gatter              | <br>Gatter, eXclusive OR, exklusives Oder – Ausgang ist genau dann logisch "1" ist, wenn an einer ungeraden Anzahl von Eingängen "1" anliegt und an den restlichen "0" |