Hierarchical Current Density Verification for Electromigration Analysis in Arbitrarily Shaped Metallization Patterns of Analog Circuits

> Göran Jerke Jens Lienig Robert Bosch GmbH Reutlingen, Germany goeran.jerke@ieee.org jens@ieee.org

### **Overview**

- Motivation and previous works

- Design flow

- How do we characterize pin currents?

- How is current density calculated?

- How do we visualize and verify current density?

- Experimental results

- Summary

## **Motivation**

Analog circuits for automotive applications

- High interconnect currents

- Ongoing reduction of circuit feature sizes, including interconnects

- Insufficiently dimensioned cross section area of interconnects

• High current densities which might lead to electromigration

### Motivation (cont.'d)

- No commercial tools available for electromigration analysis of arbitrarily shaped metallization patterns (as commonly used in analog circuits)

- Manual current density verification is very time consuming and error prone

⇒ Need for an automatic verification methodology tailored for electromigration analysis of arbitrarily shaped metallization patterns in analog circuits

### **Previous Works**

- Studies of electromigration and its relation to the mean time to failure (MTTF) of electronic circuits [Black 1969][D'Heurle 1971][Maiz 1991][Young et al. 1994]

- Electromigration analysis in digital systems [Hajj et al. 1991][Steele et al. 1998]

- Electromigration analysis in analog circuits limited to rectangular shapes [Adler et al. 2000]

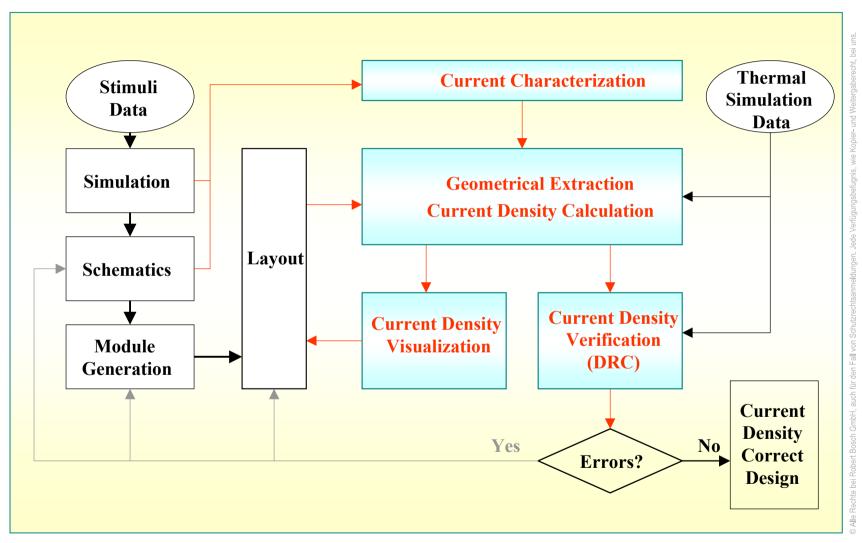

### **Design Flow**

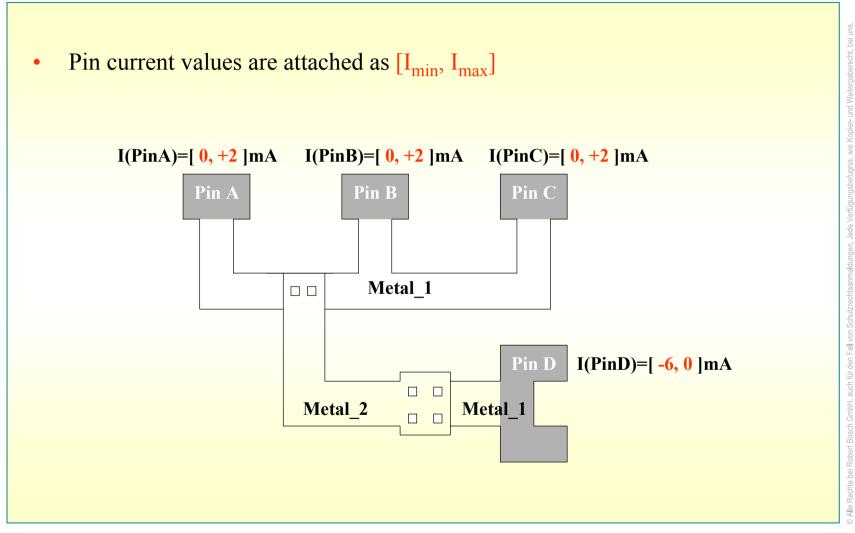

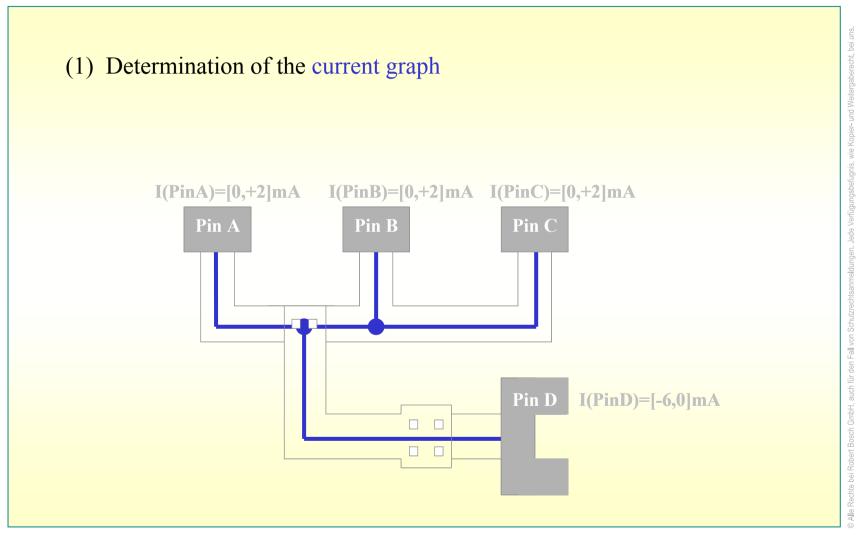

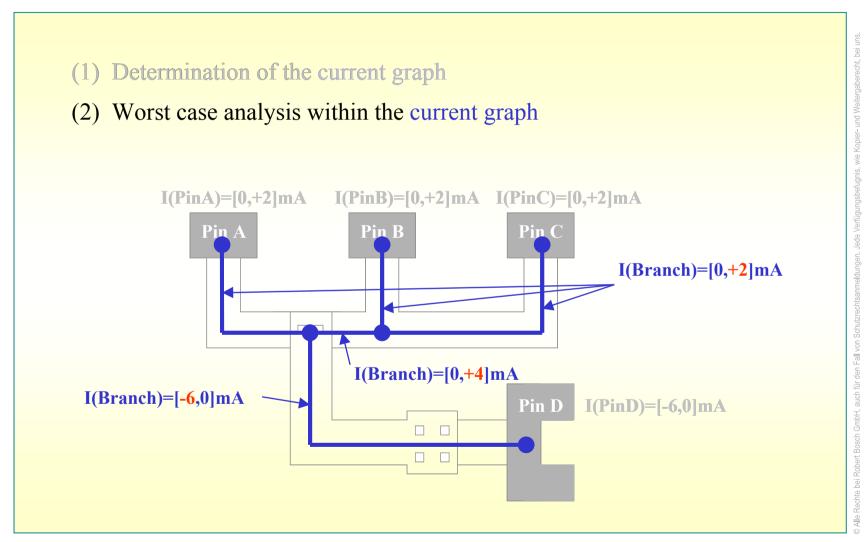

### **Pin Current Characterization**

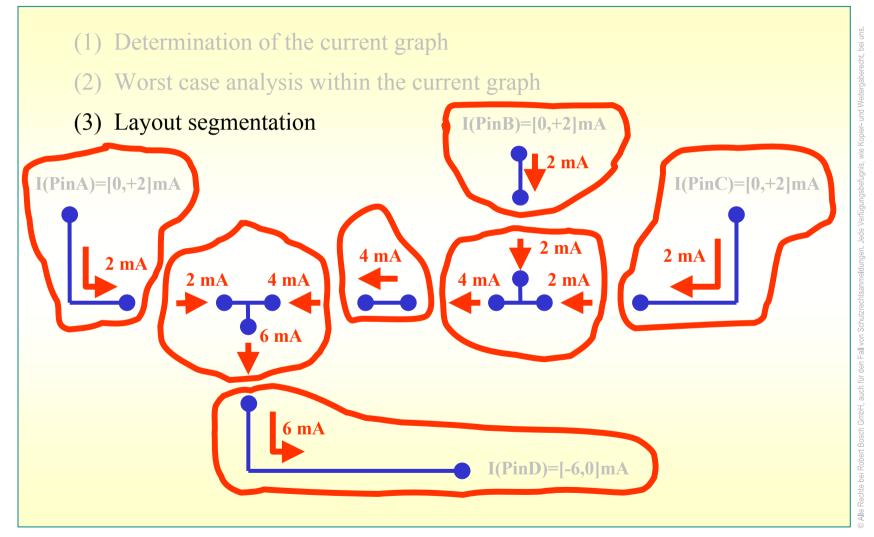

### **Layout Segmentation**

### **Layout Segmentation**

## **Layout Segmentation**

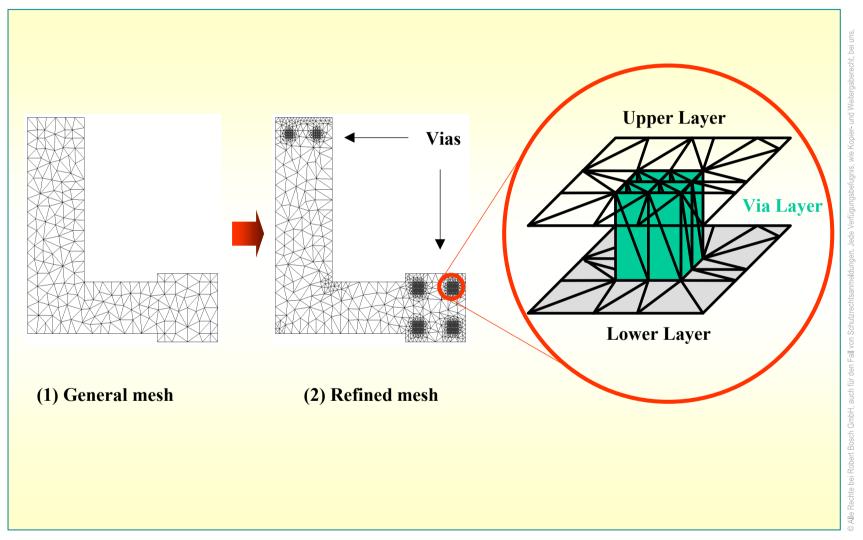

### **Geometry Extraction for Finite Element Method**

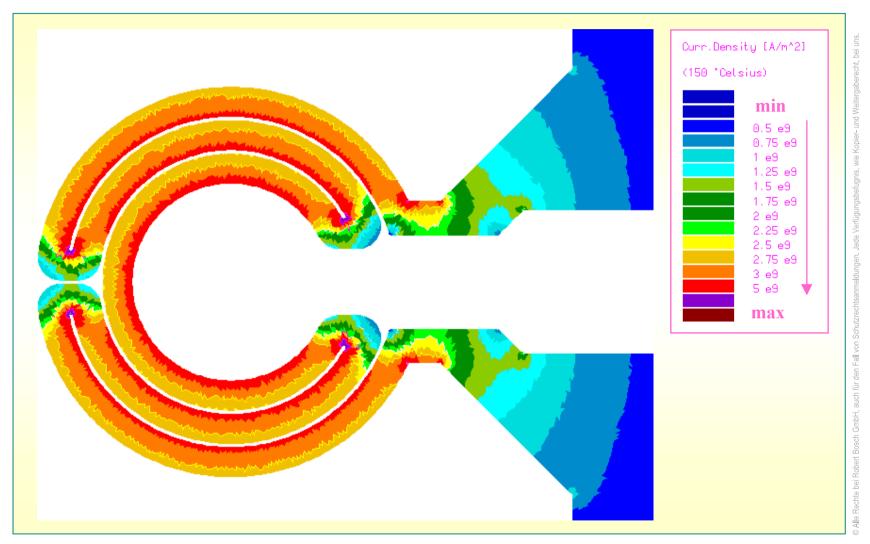

### **Current Density Calculation**

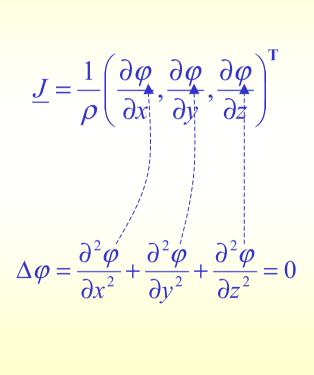

### • Given:

Segments from layout segmentation with geometry and currents

• Goal:

For each layout segment determine current density by using Maxwell's equation

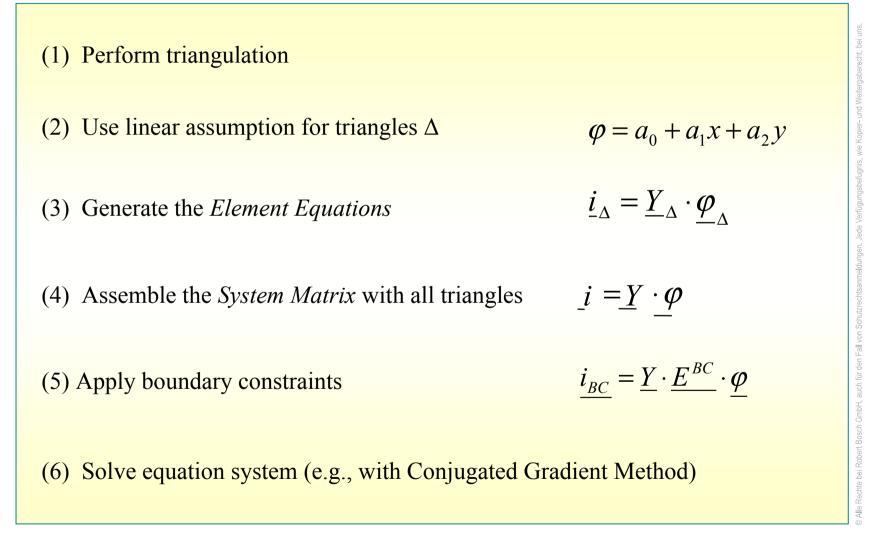

Solution: In order to obtain the potential field configuration φ(x,y,z), the Laplacian equation has to be solved using the Finite Element Method (FEM) (→ see Section 4.2 in paper)

# **Current Density Calculation: Incorporating Thermal Simulation Data**

• Problem:

Calculating current density is temperature dependent because any change in the temperature distribution influences the gradient of the electrical potential field  $\varphi(x,y,z)$

Maxwell's equation  $\underline{J} = \frac{1}{\rho} \left( \frac{\partial \varphi}{\partial x}, \frac{\partial \varphi}{\partial y}, \frac{\partial \varphi}{\partial z} \right)^{\mathrm{T}}$ • Solution: Electrical conductivity  $\rho(x, y, z)$  is determined under consideration of a thermal potential field

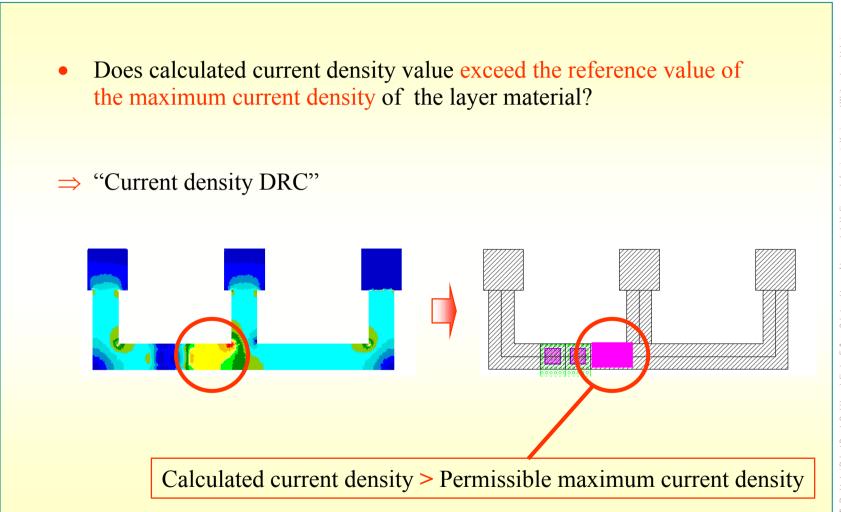

### **Current Density Verification**

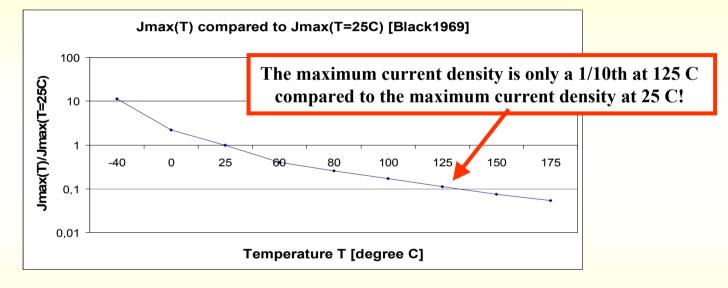

# **Current Density Verification: Incorporating Thermal Simulation Data**

• Problem:

Verifying current density is temperature dependent because acceptable maximum current varies with temperature

• Solution:

In order to verify if calculated current density is acceptable, we compare calculated current density with a reference current density scaled by the actual working temperature

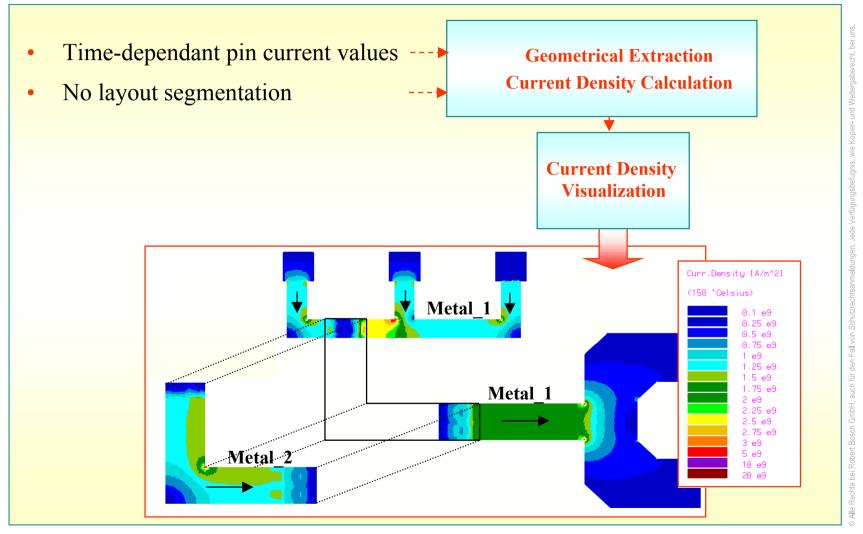

### **Current Density Visualization**

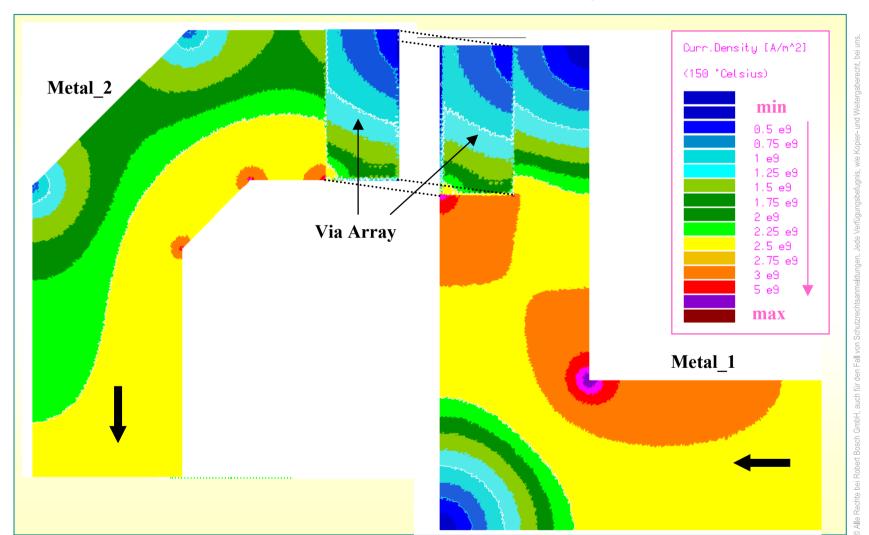

### **Results: Interconnect and Via Array**

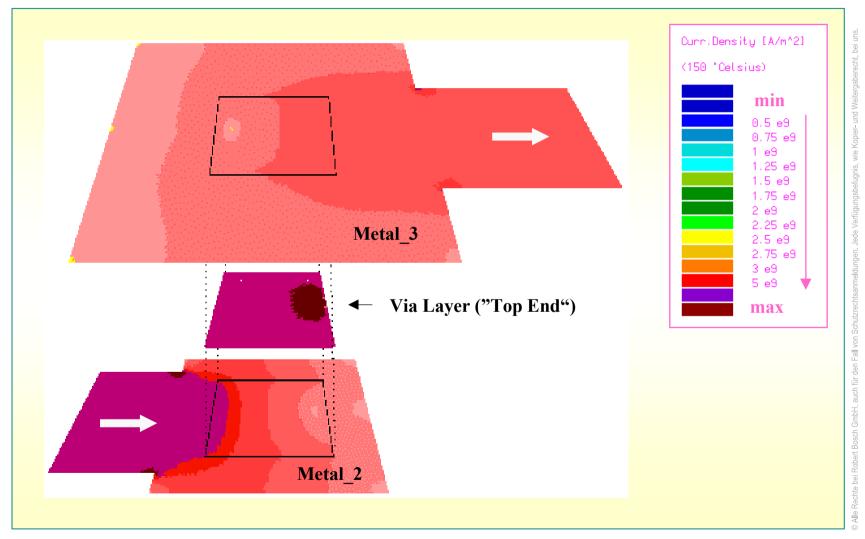

### **Results: Single Via**

### **Results: MEMS Structure**

### **Summary**

- New methodology for hierarchical verification of current densities in arbitrarily shaped analog circuit layouts

- Quasi-3D model for verifying irregularities like vias and via edge stress, using "bee-comb"-like structures

- Incorporating thermal simulation data to account for temperature dependency of electrical field configuration and electromigration

- Option of integrating our methodology as an automated current density DRC in virtually any IC-design flow

- Verification of our methodology on "real world" analog circuits

### **Appendix: Current Density Calculation (FEM)**

Jerke, G., Lienig, J: Hierarchical Current Density Verification for Electromigration Analysis in Arbitrarily Shaped Metallization Patterns of Analog Circuits, *Proceedings Design, Automation and Test in Europe (DATE)*, March 2002, pp. 464-469