Research Focus

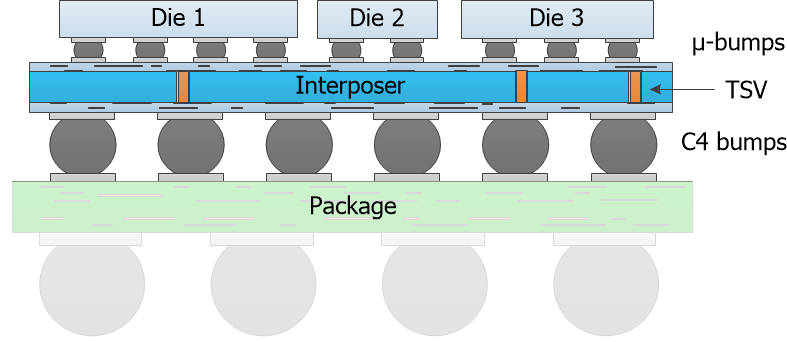

Design automation for interposer-based 3D ICs

Interposer-based 3D ICs—also known as 2.5D ICs—promise higher yield and better heat dissipation over classical 2D ICs. Such 3D ICs are currently commercially available in a few products, like FPGAs and GPUs, and they are viable contenders for the next-generation chip market. However, the designing of these products requires some notable manual intervention for placement, simulation, verification, etc.; available tools are still inadequate according to academia and industry experts.

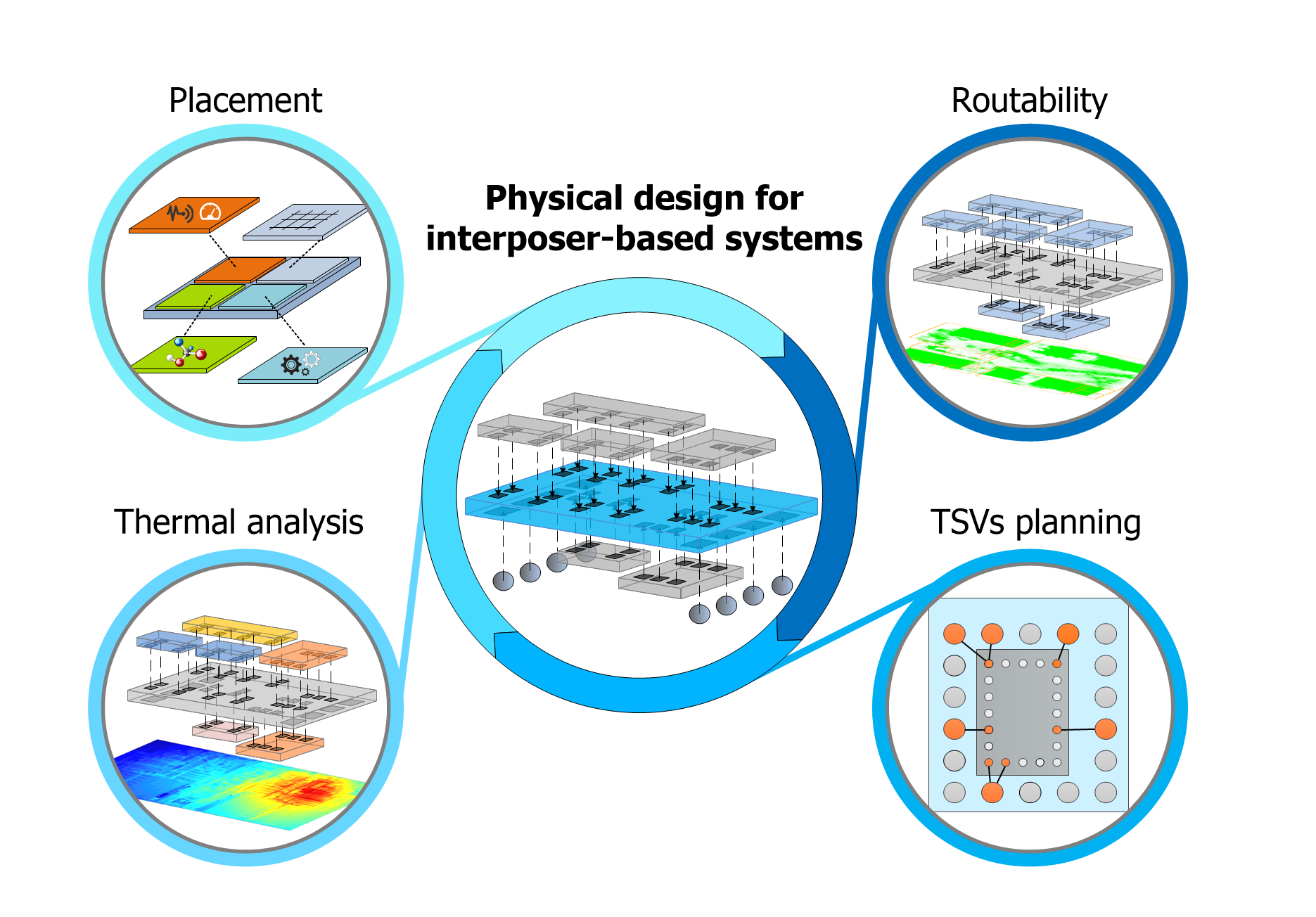

To address this issue, we are developing the automated design methodologies for interposer-based 3D ICs, including approaches for die placing,

interposer routing, thermal analysis and pin assignment.

Read our overview of design challenges for interposer-based 3D ICs

Research Interests:

Optimal Die Placement on the Interposer

We developed an effective method for optimal wirelength-driven die placement of interposer-based 3D ICs.

Our key ideas are to leverage the constraint-satisfaction problem (CSP) formalism in combination with a branch-and-bound (B&B) algorithm,

and to develop several novel techniques for early identification and pruning of unpromising configurations. Such pruning techniques

dramatically, yet accurately, confine the solution space and quickly rule out unpromising placements. Thus, we obtain optimal placement

solutions in significantly shorter runtime than prior art, and we can optimally handle larger problem instances than prior art.

Related publication

Downloads:

Corblivar 3D-Floorplanner, for planning massively parallel interconnect structures in 3D ICs

Experimentelle Software

Corblivar, latest release on GitHub

HotSpot, latest release on GitHub

Binary of the optimal interposer placement tool (supports parallel execution):

Please consider this software experimental

Binary compiled on Ubuntu 16.04 with gcc 5.4.0 (dynamically linked)

Statically linked binary compiled on Ubuntu

Benchmarks

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Contact:

Dr.-Ing. Robert Fischbach

Dr.-Ing. Andreas Krinke

Prof. Jens Lienig

German version

German version