Forschungsschwerpunkt

Entwurfsautomatisierung für Interposer-basierte 3D-ICs

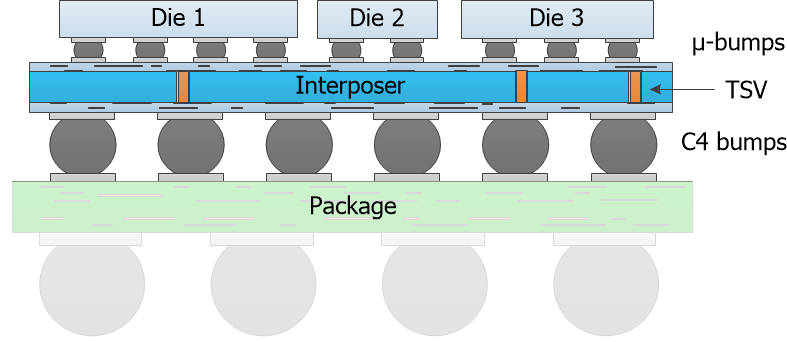

Interposer-basierte 3D-ICs – auch als 2,5D-ICs bekannt – versprechen eine höhere Ausbeute und eine bessere Wärmeableitung als klassische 2D-ICs. Solche 3D-ICs sind derzeit in einigen wenigen Produkten wie FPGAs und GPUs im Handel erhältlich und sind ernstzunehmende Kandidaten für den Chipmarkt der nächsten Generation. Die Entwicklung dieser Produkte erfordert jedoch einige erhebliche manuelle Eingriffe für die Platzierung, Simulation, Verifikation usw. Nach Ansicht von Wissenschaftlern und Branchenexperten sind die verfügbaren Tools noch unzureichend.

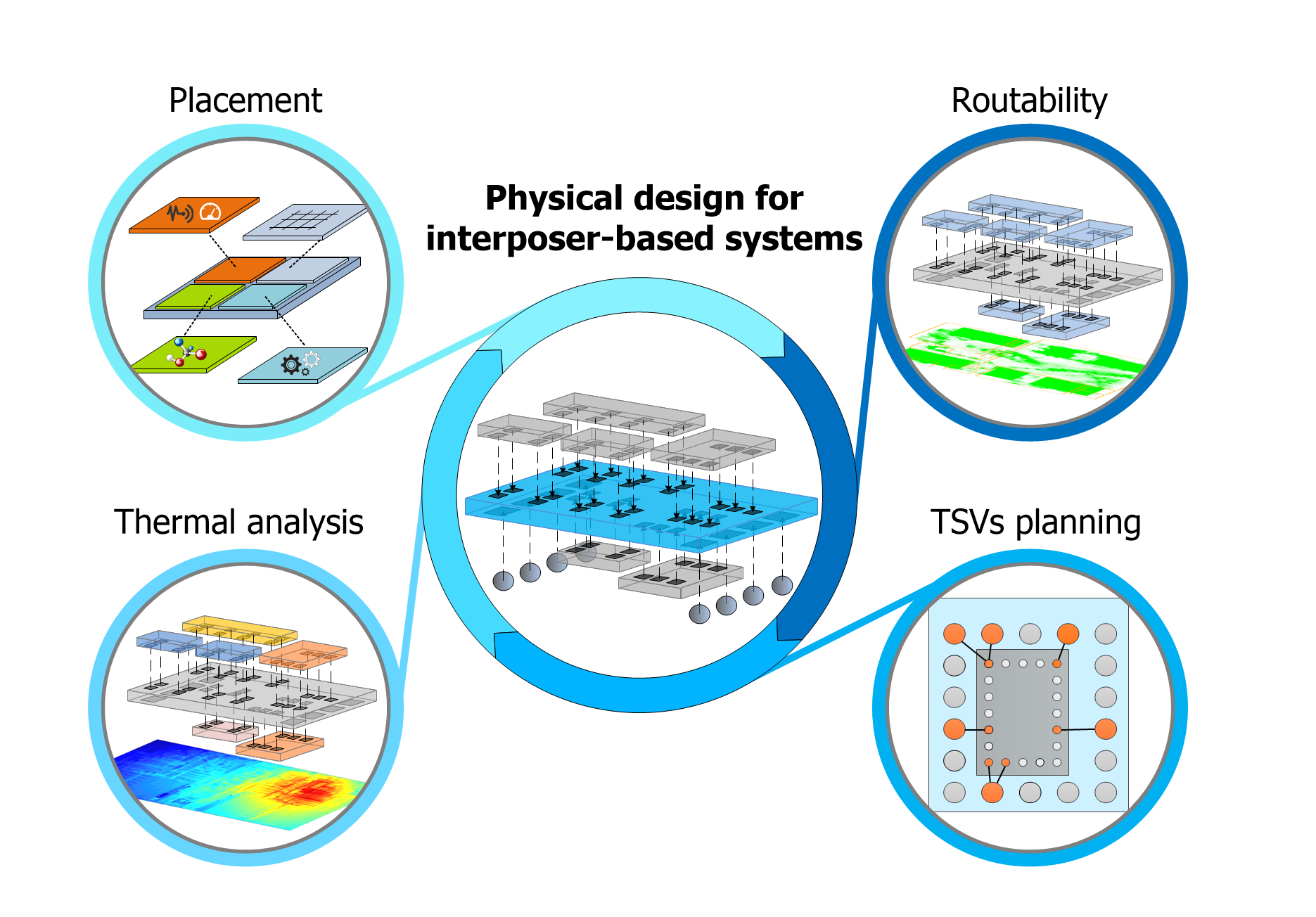

Um dieses Problem anzugehen, werden am IFTE automatisierte Entwurfsmethoden für Interposer-basierte 3D-ICs entwickelt, darunter Ansätze für die Platzierung von Chips, das Interposer-Routing, die thermische Analyse und die Pin-Zuordnung.

Hier findet sich ein Überblick über die Herausforderungen beim Entwurf von Interposer-basierten 3D-ICs.

Forschungsinteressen:

Optimale Platzierung von Chips auf einem Interposer

Am IFTE wurde eine effektive Methode für die optimale, auf der Drahtlänge basierende Platzierung von Chips in Interposer-basierten 3D-ICs entwickelt. Die Kernideen besteht darin, den Formalismus des Constraint-Satisfaction-Problems (CSP) in Kombination mit einem Branch-and-Bound-Algorithmus (B&B) zu nutzen und mehrere neuartige Techniken zur frühzeitigen Identifizierung und Eliminierung aussichtsloser Konfigurationen zu entwickeln. Solche Eliminierungstechniken schränken den Lösungsraum drastisch, aber präzise ein und schließen aussichtslose Platzierungen schnell aus. Auf diese Weise erreicht man optimale Platzierungslösungen in deutlich kürzerer Laufzeit als beim Stand der Technik und es lassen sich größere Problemfälle als beim Stand der Technik optimal bearbeiten.

Publikation mit Implementierungsdetails

Downloads:

Corblivar 3D-Floorplanner, zur Planung von massiv-parallelen Verbindungsstrukturen in 3D-ICs

Experimentelle Software:

Corblivar, neuester Stand bei GitHub

HotSpot, neuester Stand bei GitHub

Werkzeug zur optimalen Platzierung von Interposern (unterstützt parallele Ausführung)

Experimentelle Software:

Binärdatei kompiliert unter Ubuntu 16.04 mit gcc 5.4.0 (dynamisch verlinkt)

Statisch verlinkte Binärdatei kompiliert unter Ubuntu

Benchmarks

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Anpsrechpartner:

Dr.-Ing. Robert Fischbach

Dr.-Ing. Andreas Krinke

Prof. Jens Lienig

Englische Version

Englische Version